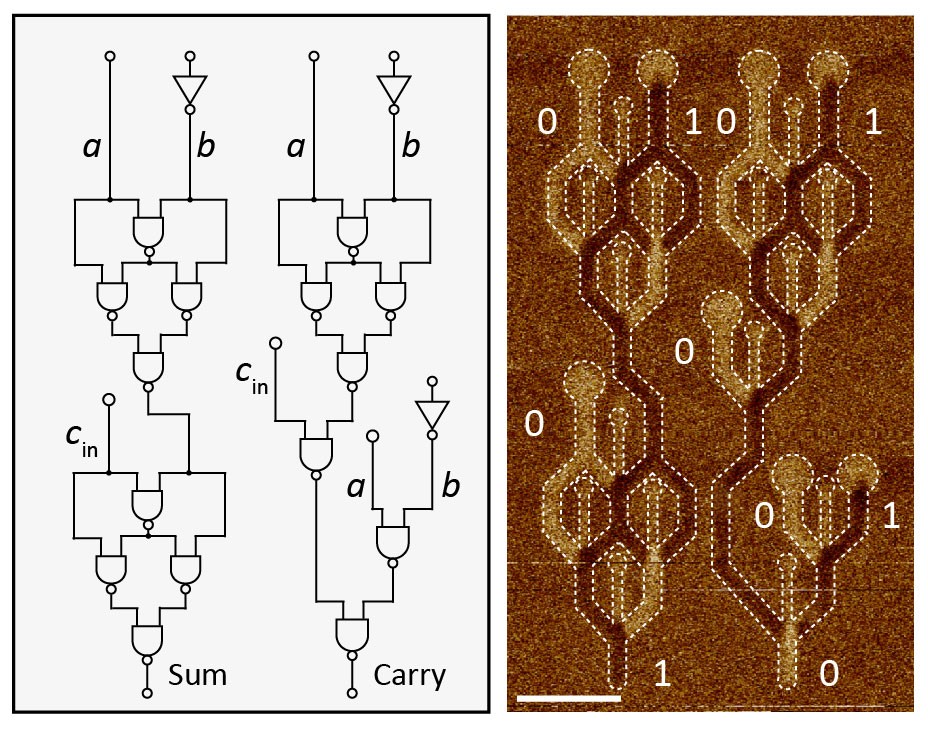

Figure 8 | Design and simulation of an all optical full-adder based on photonic crystals | SpringerLink

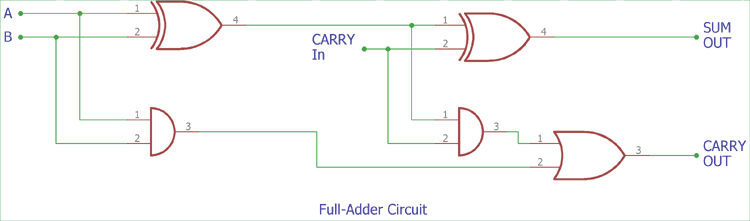

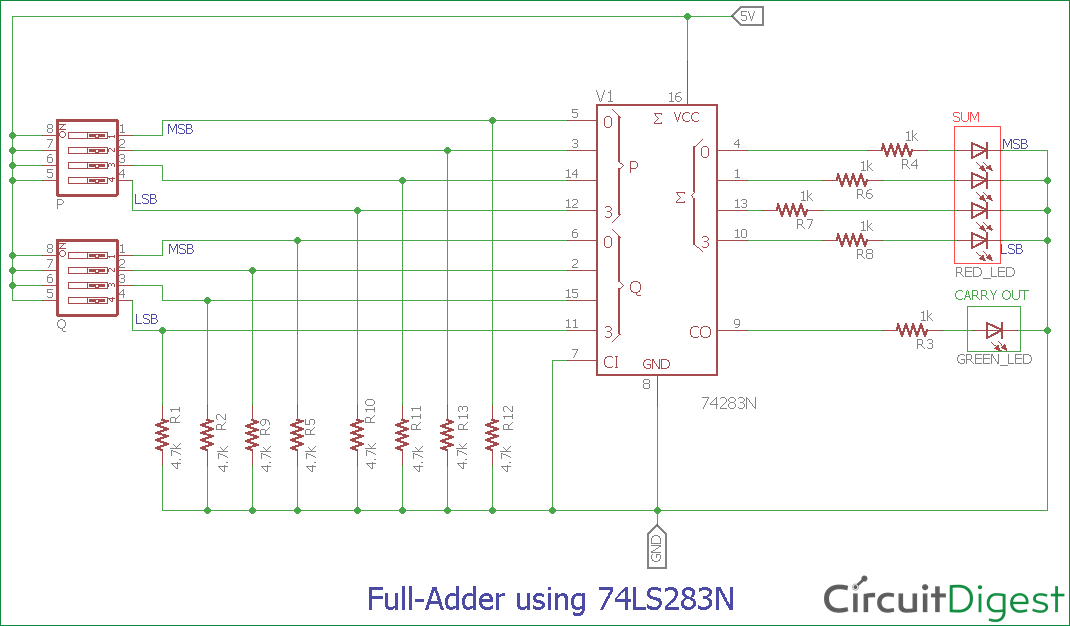

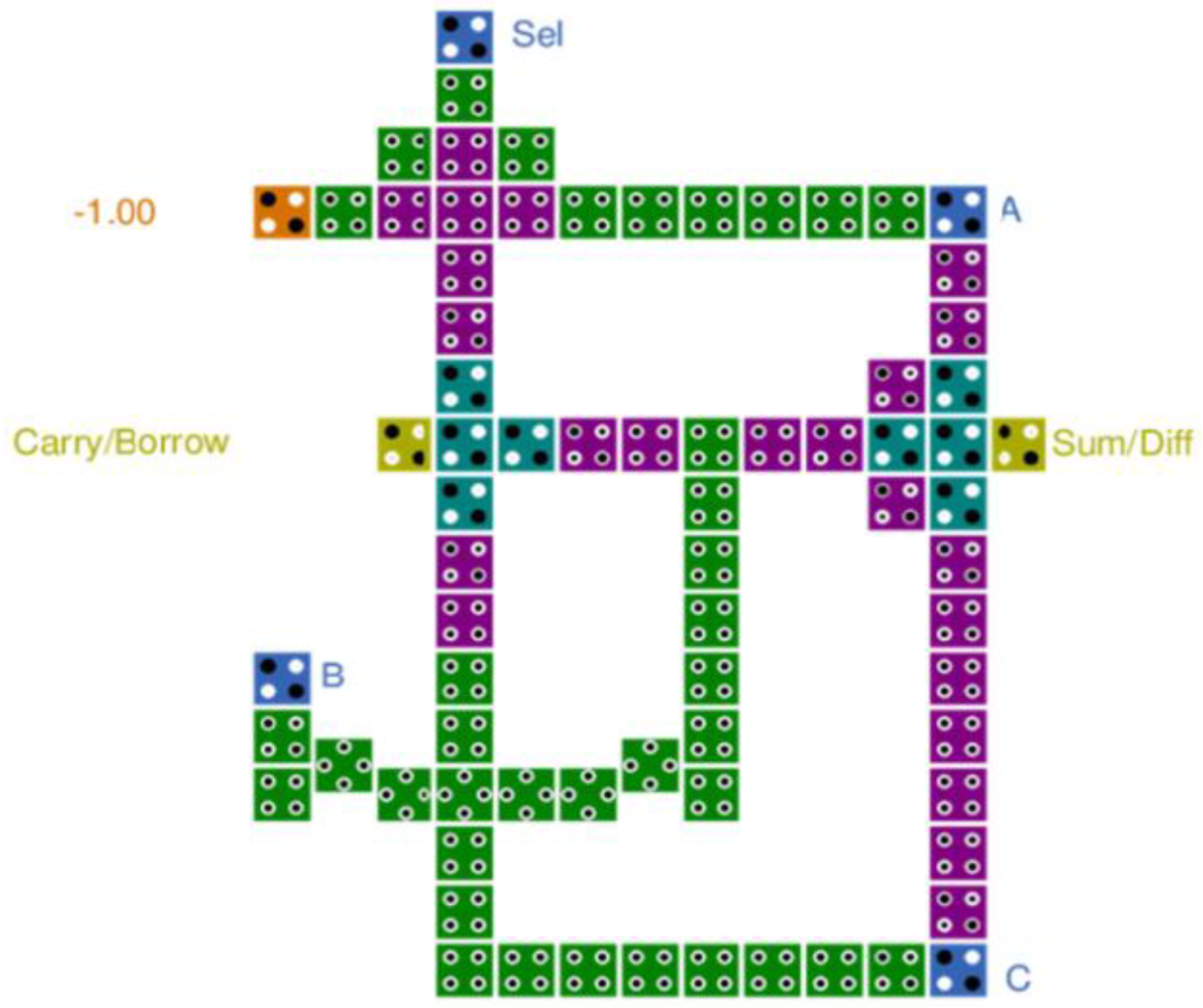

Applied Sciences | Free Full-Text | Design and Implementation of Novel Efficient Full Adder/Subtractor Circuits Based on Quantum-Dot Cellular Automata Technology | HTML

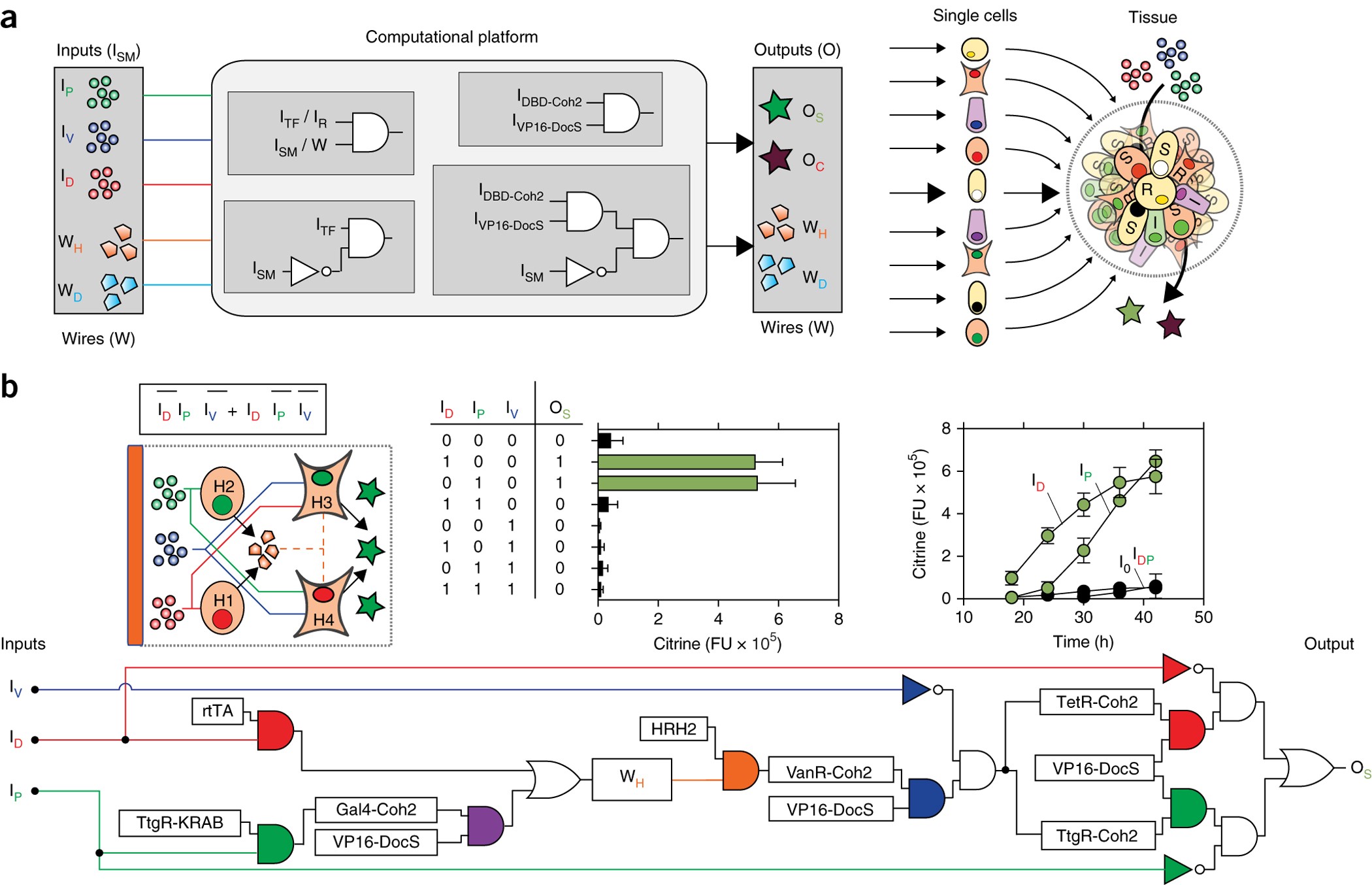

Programmable full-adder computations in communicating three-dimensional cell cultures | Nature Methods

PDF) An Ultra-High-Speed Low-Power CMOS 1-Bit Fast Full Adder Cell Using Gate-Diffusion Input Technique | jovial s - Academia.edu

Fast and High-Performing 1-Bit Full Adder Circuit Based on Input Switching Activity Patterns and Gate Diffusion Input Technique | SpringerLink